एफपीजीए

फिल्ड-प्रोग्रामेबल गेट अरे या एफपीजीए (FPGA) एक विशेष प्रकार का अंकीय एकीकृत परिपथ है जिसे प्रयोक्ता अपनी आवश्यकतानुसार विन्यासित करके विविध प्रकार के कार्य करा सकता है। विन्यास करने के लिये प्रोग्राम करना पड़ता है। चूँकि निर्माण के बाद प्रयोक्ता द्वारा इसकी आन्तरिक बनावट को बदला जा सकता है, इसलिये इसे 'फिल्ड प्रोग्रामेबल' कहते हैं। एफपीजीए का प्रयोग करके वे सारे लॉजिकल कार्य किये/कराये जा सकते हैं जो 'एसिक' (ASICs) द्वारा किये जाते हैं।

तकनीकी डिजाइन

[संपादित करें]

इतिहास

[संपादित करें]21 वीं सदी के विकास

[संपादित करें]समयसीमा

[संपादित करें]गेट्स

[संपादित करें]प्रमुख एफपीजीए निर्माता कंपनियाँ

[संपादित करें]एफपीजीए में प्रयुक्त आधारभूत प्रौद्योगिकियाँ

[संपादित करें]- SRAM - based on static memory technology. In-system programmable and re-programmable. Requires external boot devices. CMOS.

- Antifuse - One-time programmable. CMOS.

- PROM - Programmable Read-Only Memory technology. One-time programmable because of plastic packaging.

- EPROM - Erasable Programmable Read-Only Memory technology. One-time programmable but with window, can be erased with ultraviolet (UV) light. CMOS.

- EEPROM - Electrically Erasable Programmable Read-Only Memory technology. Can be erased, even in plastic packages. Some but not all EEPROM devices can be in-system programmed. CMOS.

- Flash - Flash-erase EPROM technology. Can be erased, even in plastic packages. Some but not all flash devices can be in-system programmed. Usually, a flash cell is smaller than an equivalent EEPROM cell and is therefore less expensive to manufacture. CMOS.

- Fuse - One-time programmable. Bipolar.

तुलना

[संपादित करें]अन्य प्रोग्रामीय युक्तियाँ

[संपादित करें]एफपीजीए के अतिरिक्त अन्य प्रकार की युक्तियाँ भी हैं जिन्हें निर्माण के बाद प्रोग्राम करके काम में लिया जाता है। वे हैं -

- PLD (प्रोग्रामेबल लॉजिक डिवाइस, प्रोग्रामेबल लॉजिक सर्किट), PLD (प्रोग्रामेबल लॉजिक डिवाइस, प्रोग्रामेबल लॉजिक सर्किट)

- EPLD (मिटाने योग्य प्रोग्रामेबल लॉजिक डिवाइस, प्रोग्रामेबल लॉजिक सर्किट और मिटाने योग्य), EPLD (मिटाने योग्य प्रोग्रामेबल लॉजिक डिवाइस, और मिटाने योग्य प्रोग्रामेबल लॉजिक सर्किट)

- CPLD (जटिल प्रोग्रामेबल लॉजिक डिवाइस, जटिल प्रोग्रामेबल लॉजिक सर्किट), CPLD (जटिल प्रोग्रामेबल लॉजिक डिवाइस, जटिल प्रोग्रामेबल लॉजिक सर्किट)

- PAL (प्रोग्रामेबल एरे लॉजिक, प्रोग्रामेबल लॉजिक एरे), PAL (प्रोग्रामेबल एरे लॉजिक, प्रोग्रामेबल लॉजिक एरे)

- PLA (प्रोग्रामेबल लॉजिक एरे, प्रोग्रामेबल लॉजिक एरे), PLA (प्रोग्रामेबल लॉजिक एरे, प्रोग्रामेबल लॉजिक एरे)

जटिल प्रोग्राम करने योग्य तर्क डिवाइस (सीपीएलडी)

[संपादित करें]सुरक्षा विचार

[संपादित करें]आवेदन

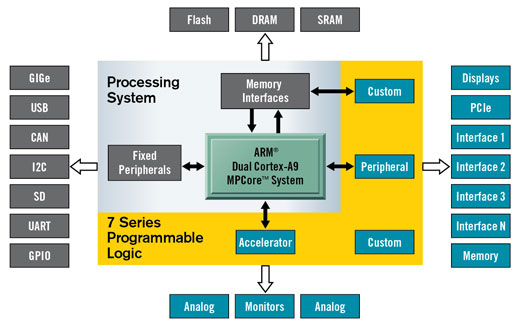

[संपादित करें]आर्किटेक्चर

[संपादित करें]लॉजिक ब्लॉक

[संपादित करें]हार्ड ब्लॉक

[संपादित करें]क्लॉकिंग

[संपादित करें]3 डी आर्किटेक्चर

[संपादित करें]एफपीजीए की डिजाइन और प्रोग्रामिंग

[संपादित करें]प्रयोक्ता हार्डवेयर डिस्क्रिप्शन लैंगवेज एचडीएल में या स्कीमैटिक आरेख द्वारा एफपीजीए से अपेक्षित व्यवहार की डिजाइन करता है। बडे डिजाइनों में एचडीएल में काम करना सुविधाजनक होता है जबकि छोटे डिजाइनों के लिये स्कीमैटिक आरेख उपयुक्त है।[1]

इसके बाद किसी ईडीए टूल का उपयोग करके 'टेक्नॉलोजी-मैप्प्ड नेटलिस्ट' जनरेट की जाती है। इसके बाद 'प्लेस-एण्ड-रूट' प्रक्रिया द्वारा इस नेटलिस्ट को एफ्पीजीए में उतारा जाता है। प्रयोक्ता मैपिंग तथा 'प्लेस ऐण्ड रूट' के परिणामों की सत्यता की जाँच (वैलिडेशन) करने के लिये सिमुलेशन तथा टाइमिंग एनालिसिस]] आदि का सहारा लेता है। जब वह आश्वस्त हो जाता है तो पूर्व प्रक्रिया में उत्पन्न बाइनरी फाइल का उपयोग करते हुए एफपीजीए को 'री-कॉनफिगर' कर दिया जाता है। यह फाइल एफपीजीए में सीरियल इंटरफेस (JTAG/जेटैग) के द्वारा या किसी बाहरी ईप्रोम स्मृति में स्थानान्तरित कर दी जाती है।[2]

बाहरी कड़ियाँ

[संपादित करें]| यह लेख एक आधार है। जानकारी जोड़कर इसे बढ़ाने में विकिपीडिया की मदद करें। |

- ↑ Wisniewski, Remigiusz (2009). Synthesis of compositional microprogram control units for programmable devices. Zielona Góra: University of Zielona Góra. पृ॰ 153. आई॰ऍस॰बी॰ऍन॰ 978-83-7481-293-1.[मृत कड़ियाँ]

- ↑ "FPGA Architecture for the Challenge". toronto.edu. मूल से 11 मई 2018 को पुरालेखित. अभिगमन तिथि 2 मई 2018.